#### Chapter 4

### Computer Architecture

Bocos Benedict/ShutterStock, Inc. Copyright © 2017 by Jones & Bartlett Learning, LLC an Ascend Learning Company www.jblearning.com

# Pep/9 virtual machine

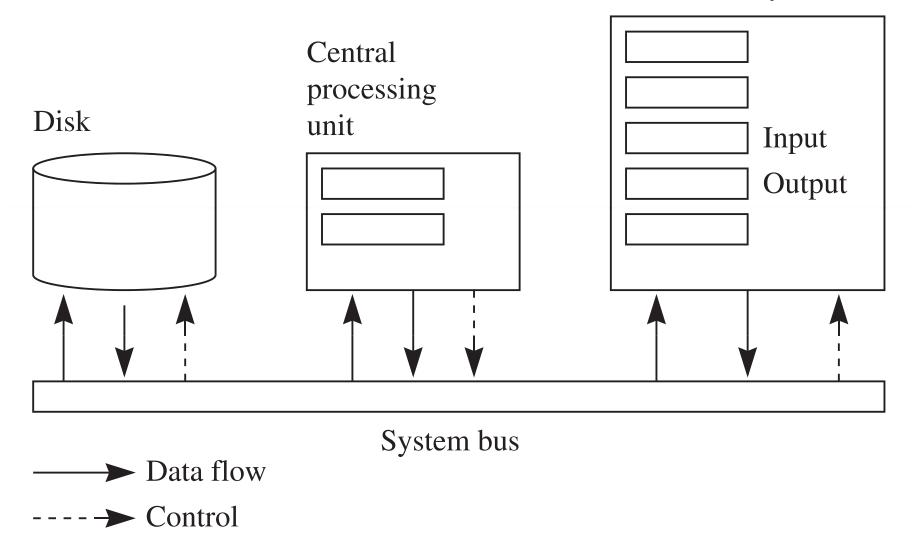

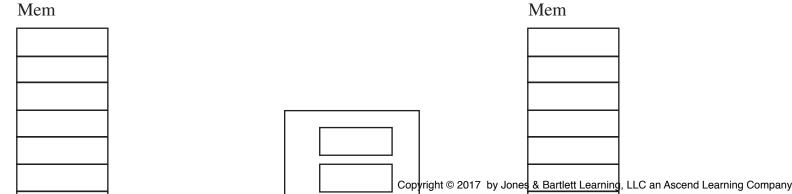

#### Main memory

Copyright © 2017 by Jones & Bartlett Learning, LLC an Ascend Learning Company

Figure 4.2

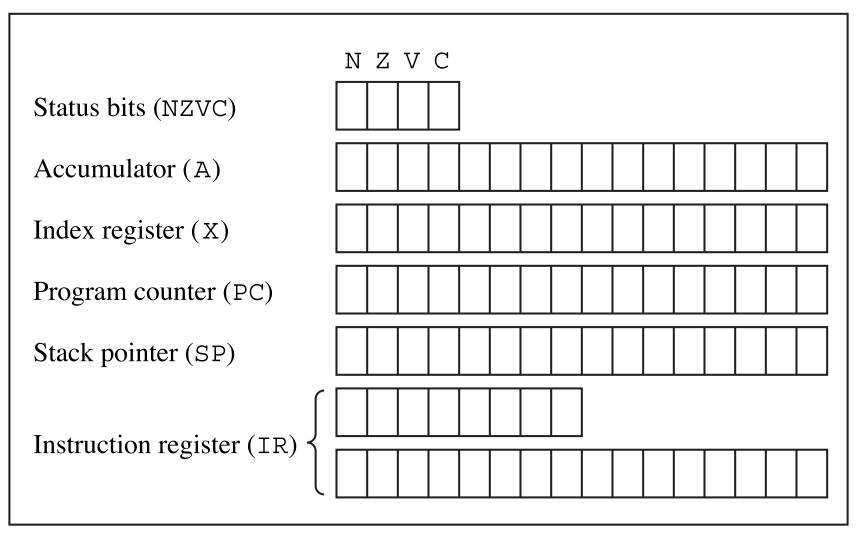

#### Central processing unit (CPU)

Figure 4.3

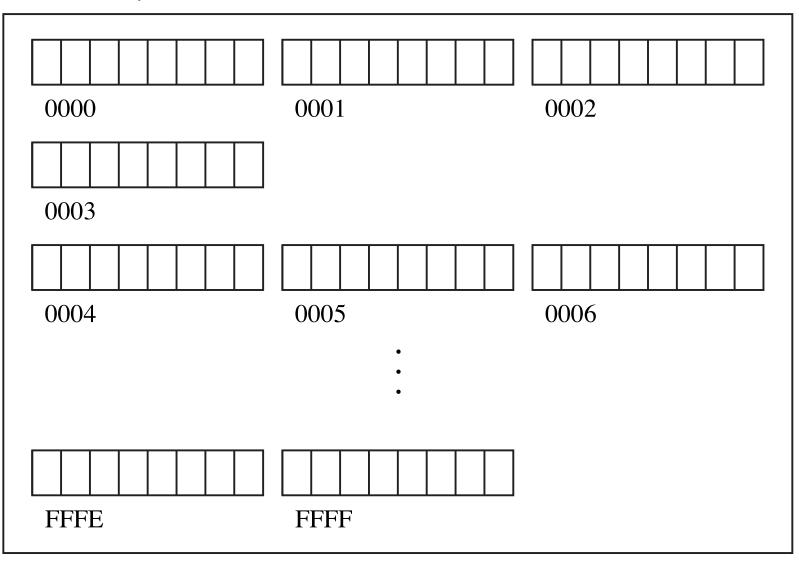

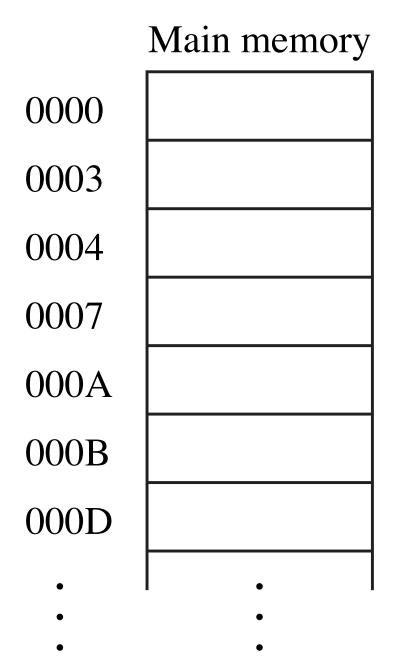

#### Main memory

Figure 4.4

Figure 4.5

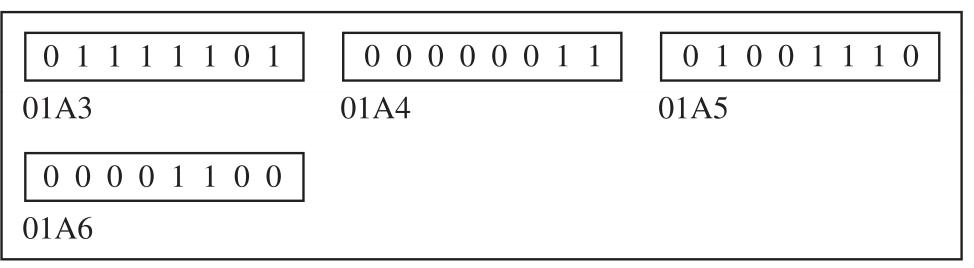

000B

000C

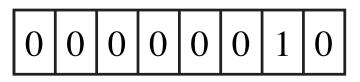

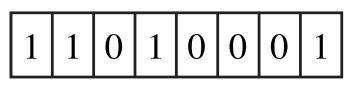

(a) The content in binary.

| 02   | D1   |  |

|------|------|--|

| 000B | 000C |  |

(b) The content in hexadecimal.

000B 02D1(c) The content in a machine language listing.

| Instruction Specifier | Instruction                                 |

|-----------------------|---------------------------------------------|

| 0000 0000             | Stop execution                              |

| 0000 0001             | Return from CALL                            |

| 0000 0010             | Return from trap                            |

| 0000 0011             | Move SP to A                                |

| 0000 0100             | Move NZVC flags to A $\langle 1215 \rangle$ |

| 0000 0101             | Move A(1215) to NZVC flags                  |

| 0000 011r             | Bitwise invert r                            |

| 0000 100r             | Negate r                                    |

| 0000 101r             | Arithmetic shift left r                     |

| 0000 110r             | Arithmetic shift right r                    |

| 0000 111r             | Rotate left r                               |

| 0001 000r             | Rotate right r                              |

Figure 4.6 (continued)

| 0001 001a<br>0001 010a<br>0001 011a<br>0001 100a<br>0001 101a<br>0001 111a<br>0010 000a<br>0010 001a<br>0010 010a | Branch unconditional<br>Branch if less than or equal to<br>Branch if less than<br>Branch if equal to<br>Branch if not equal to<br>Branch if greater than or equal to<br>Branch if greater than<br>Branch if V<br>Branch if C<br>Call subroutine |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0010 011n                                                                                                         | Unimplemented opcode, unary trap                                                                                                                                                                                                                |

| 0010 1aaa<br>0011 0aaa<br>0011 1aaa<br>0100 0aaa<br>0100 1aaa                                                     | Unimplemented opcode, nonunary trap<br>Unimplemented opcode, nonunary trap<br>Unimplemented opcode, nonunary trap<br>Unimplemented opcode, nonunary trap<br>Unimplemented opcode, nonunary trap                                                 |

Figure 4.6 (continued)

| 0101 0aaa | Add to stack pointer (SP)        |

|-----------|----------------------------------|

| 0101 1aaa | Subtract from stack pointer (SP) |

| 0110 raaa | Add to r                         |

| 0111 raaa | Subtract from r                  |

| 1000 raaa | Bitwise AND to r                 |

| 1001 raaa | Bitwise OR to r                  |

| 1010 raaa | Compare word to r                |

| 1011 raaa | Compare byte to r(815)           |

| 1100 raaa | Load word r from memory          |

| 1101 raaa | Load byte r(815) from memory     |

| 1110 raaa | Store word r to memory           |

| 1111 raaa | Store byte r(815) to memory      |

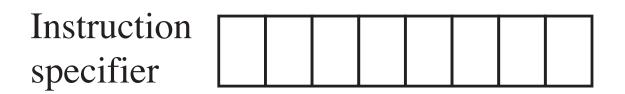

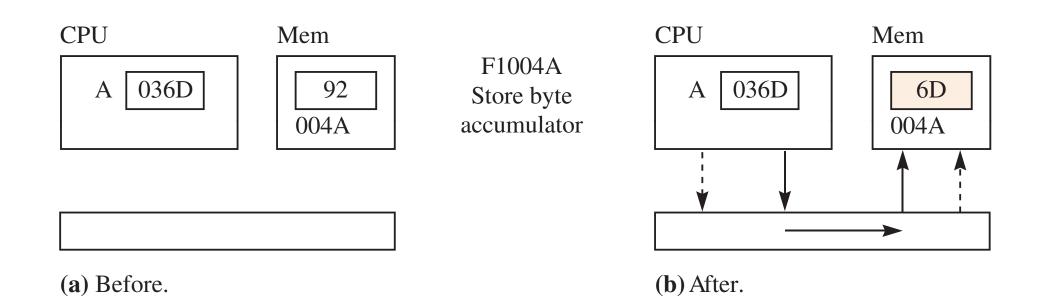

Figure 4.7

Operand specifier

(a) The two parts of a nonunary instruction

Instruction specifier

(b) A unary instruction

Figure 4.8

| aaa     | Addressing Mode         |

|---------|-------------------------|

| 000     | Immediate               |

| 001     | Direct                  |

| 010     | Indirect                |

| 011     | Stack-relative          |

| 100     | Stack-relative deferred |

| 101     | Indexed                 |

| 110     | Stack-indexed           |

| 111     | Stack-deferred indexed  |

| a) That | addressing-222 field    |

(a) The addressing-aaa field.

| а                           | Addressing Mode | r                         | Register          |

|-----------------------------|-----------------|---------------------------|-------------------|

| 0                           | Immediate       | 0                         | Accumulator, A    |

| 1                           | Indexed         | 1                         | Index register, X |

| (b) The addressing-a field. |                 | (c) The register-r field. |                   |

Figure 4.9

#### Main memory

# Direct addressing

- Oprnd = Mem[OprndSpec]

- The operand specifier is the memory address of the operand.

## The stop instruction

- Instruction specifier: 0000 0000

- Causes the computer to stop

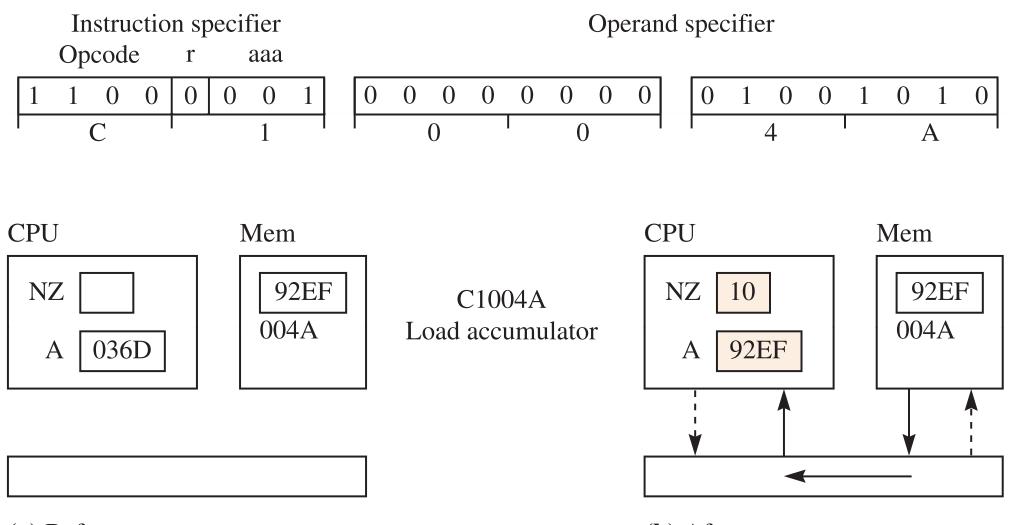

# The load word instruction

- Instruction specifier: 1100 raaa

- Loads one word (two bytes) from memory to register r

### $r \leftarrow Oprnd$ ; $N \leftarrow r < 0$ , $Z \leftarrow r = 0$

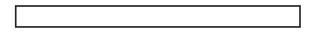

Figure 4.10, 4.11

(a) Before.

(**b**) After.

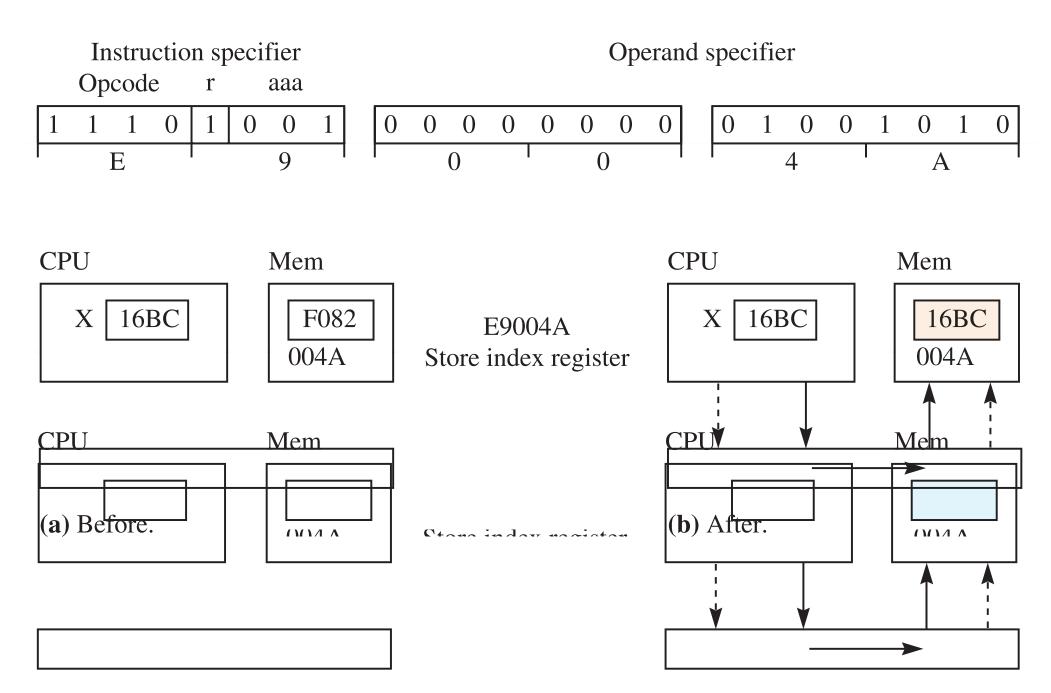

## The store word instruction

- Instruction specifier: 1110 raaa

- Stores one word (two bytes) from register r to memory

$Oprnd \leftarrow r$

$\mathbf{0}$

(a) Before

(dy) ght for a py Jones & Bartlett Learning, LLC an Ascend Learning Company

$\frac{\mathbf{Figure}^{1} \mathbf{4.92, }^{1} \mathbf{4.13}}{A}$

0

4

### The add instruction

- Instruction specifier: 0110 raaa

- Adds one word (two bytes) from memory to register r

$$\begin{aligned} r \leftarrow r + Oprnd \; ; \; N \leftarrow r < 0 \; , \; Z \leftarrow r = 0 \; , \\ V \leftarrow \{ \textit{overflow} \} \; , \; C \leftarrow \{ \textit{carry} \} \end{aligned}$$

mputer Systems FIFTH EDITION (Figure 4.04, 14.165 0 4 А Instruction specifier Operand specifier Opcode r aaa 1 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 1 1 1 0 0 0 9 6 0 0 4 A CPU CPU Mem Mem NZVC NZVC 1000 FFF9 FFF9 69004A 004A 004A Add index register 0005 FFFE Χ Х CPŲ CPU Mem Mem 1 ΛΛΛ Λ A dd in dan na sistan (**b**) After. (a) Before.

Copyright © 2017 by Jones & Bartlett Learning, LLC an Ascend Learning Corhpany

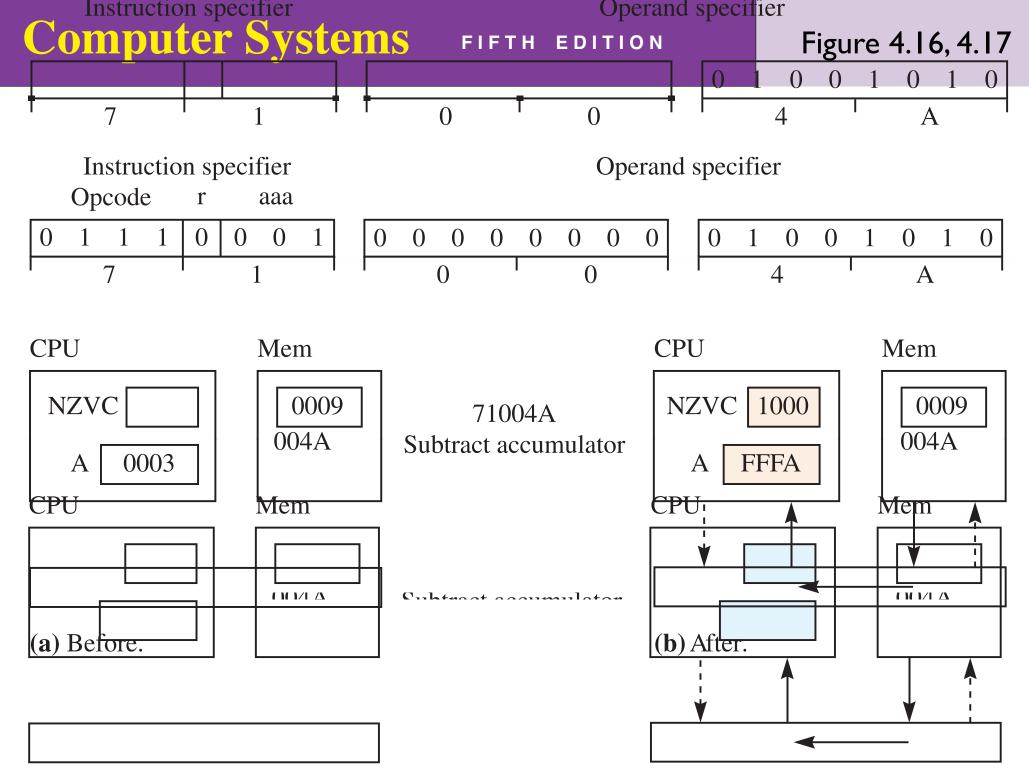

### The subtract instruction

- Instruction specifier: 0111 raaa

- Subtracts one word (two bytes) from memory from register r

$$\begin{split} r \leftarrow r - Oprnd \; ; \; N \leftarrow r < 0 \; , \; Z \leftarrow r = 0 \; , \\ V \leftarrow \{ \textit{overflow} \} \; , \; C \leftarrow \{ \textit{carry} \} \end{split}$$

(a) Refore

Copyright 0,2017 by Jones & Bartlett Learning, LLC an Ascend Learning Company

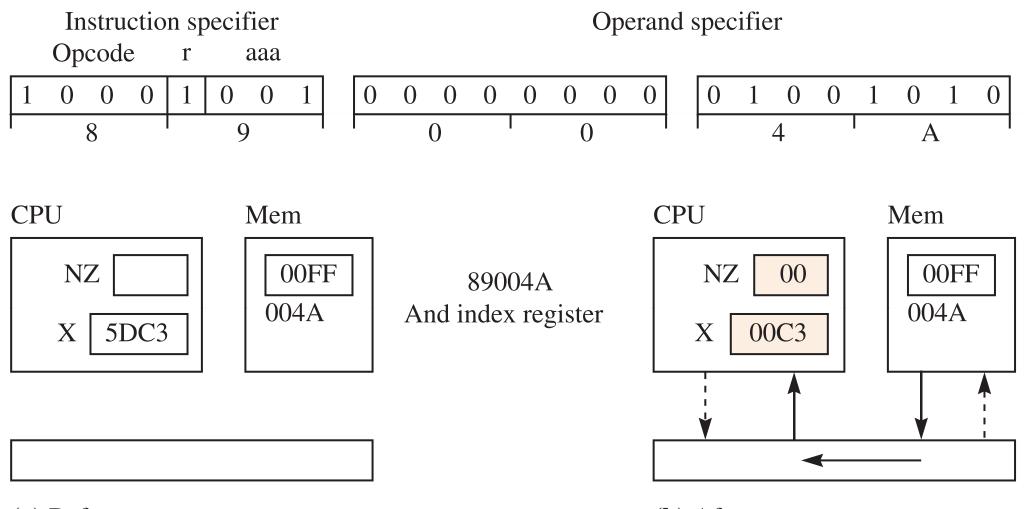

### The and instruction

- Instruction specifier: 1000 raaa

- ANDs one word (two bytes) from memory to register r

$r \leftarrow r \wedge Oprnd$  ; N  $\leftarrow r < 0$  , Z  $\leftarrow r = 0$

Figure 4.18, 4.19

(a) Before.

(**b**) After.

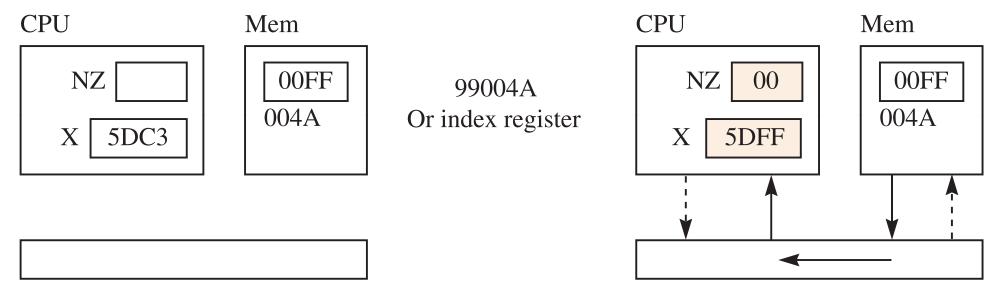

### The or instruction

- Instruction specifier: 1001 raaa

- ORs one word (two bytes) from memory to register r

$r \leftarrow r \lor Oprnd$  ; N  $\leftarrow r < 0$  , Z  $\leftarrow r = 0$

### (a) Before. (b) After. (b) After.

#### Figure 4.20

(a) Before.

(**b**) After.

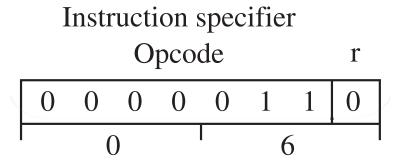

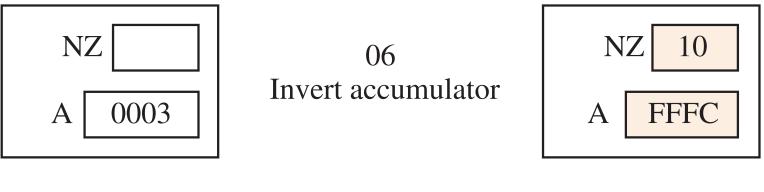

### The invert instruction

- Instruction specifier: 0000 011r

- Bit-wise NOT operation on register r

- Each 0 changed to 1, each 1 changed to 0

### $r \leftarrow \neg r \ ; \ N \leftarrow r < 0 \ , \ Z \leftarrow r = 0$

Figure 4.21, 4.22

(a) Before.

(**b**) After.

# The negate instruction

- Instruction specifier: 0000 100r

- Negate (take two's complement of) register r

### $r \leftarrow -r \ ; \ N \leftarrow r < 0 \ , \ Z \leftarrow r = 0$

(b) After.

Copyright © 2017 by Jones & Bartlett Learning, LLC an Ascend Learning Company

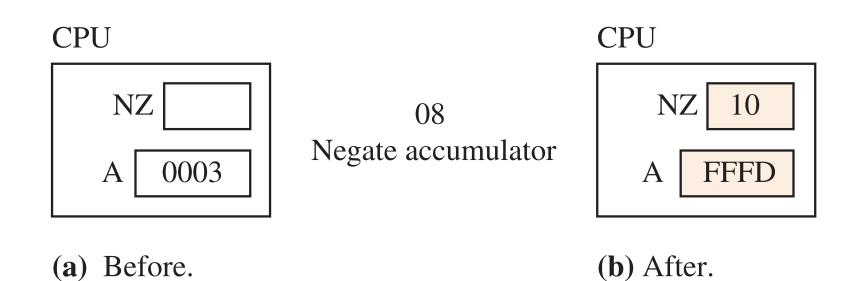

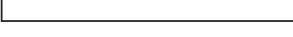

# The load byte instruction

- Instruction specifier: 1101 raaa

- Loads one byte from memory to the right half of register r

$r\langle 8..15 \rangle \leftarrow byte \ Oprnd ; N \leftarrow 0 , Z \leftarrow r\langle 8..15 \rangle = 0$

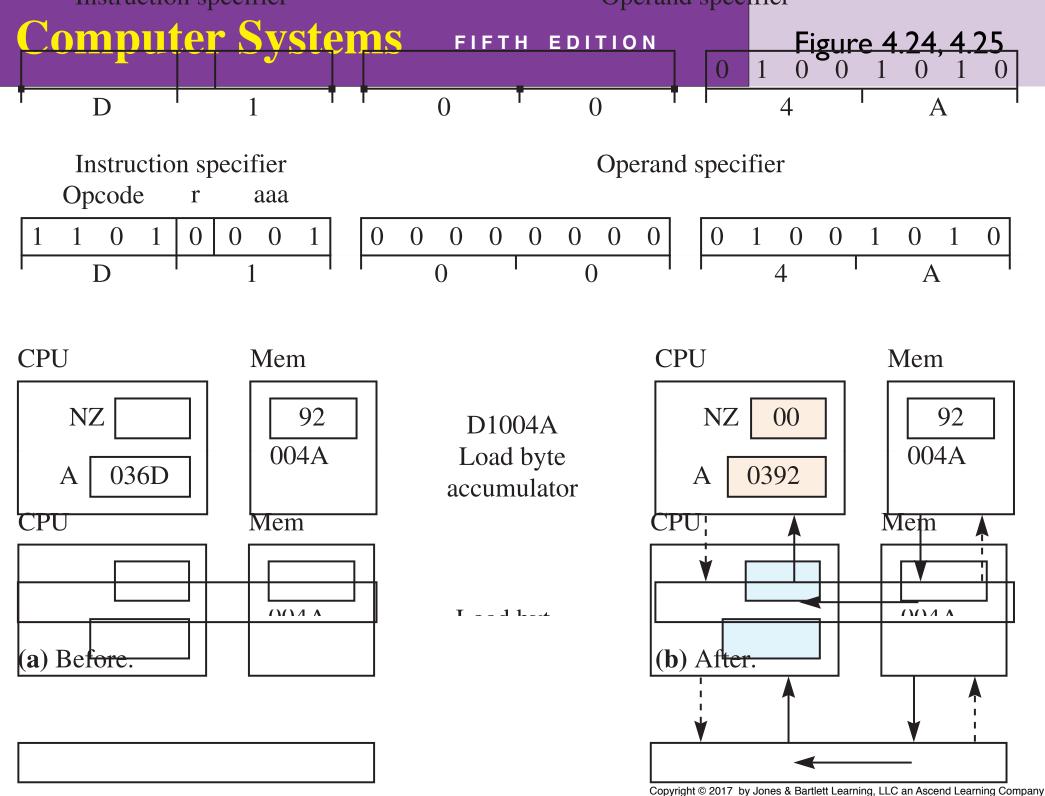

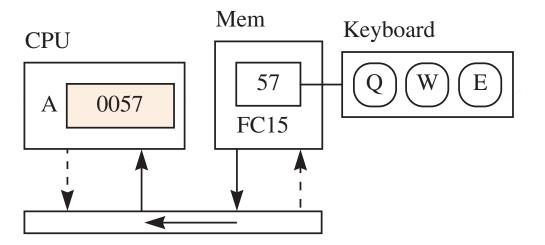

# The store byte instruction

- Instruction specifier: IIII raaa

- Stores one byte from the right half of register r to memory

byte Oprnd

$$\leftarrow r(8..15)$$

Figure 4.27

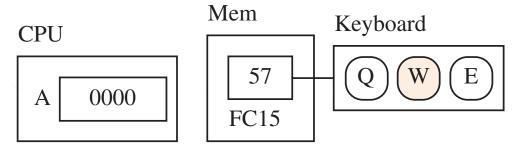

# Load byte from input device

(a) Before.

(b) After.

## Store byte to output device

(a) Before.

Figure 4.29

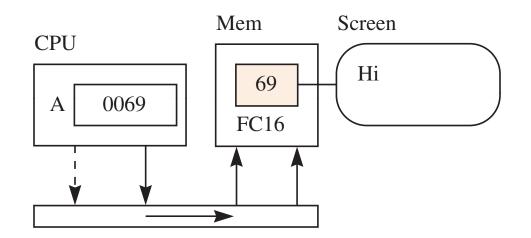

## A little-endian CPU

(a) Before.

(**b**) After.

Figure 4.30

# A 32-bit register load

|             | Initial State | Big Endian<br>Final State | Little Endian<br>Final State |

|-------------|---------------|---------------------------|------------------------------|

| Mem[019E]   | 89            | 89                        | 89                           |

| Mem[019F]   | AB            | AB                        | AB                           |

| Mem[01A0]   | CD            | CD                        | CD                           |

| Mem[01A1]   | EF            | EF                        | EF                           |

| Accumulator |               | 89 AB CD EF               | EF CD AB 89                  |

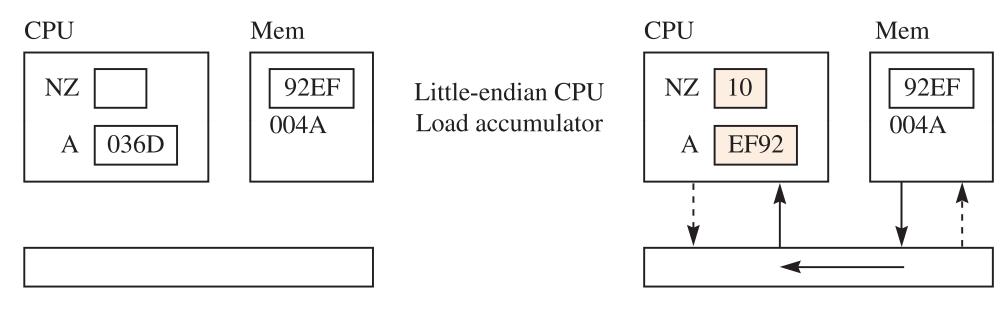

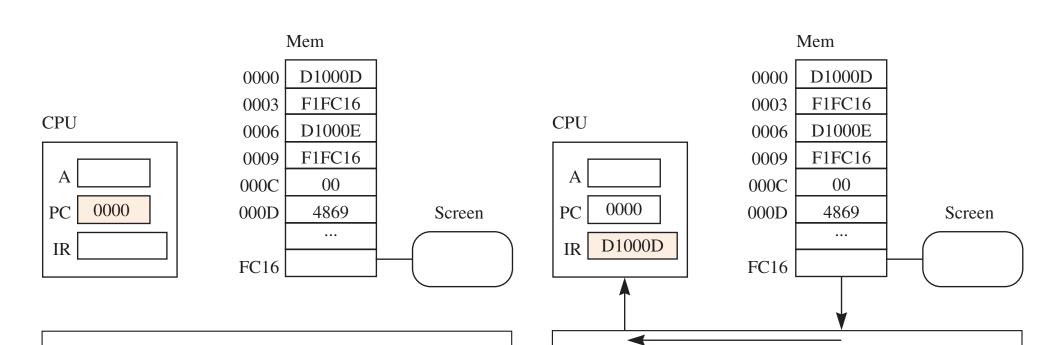

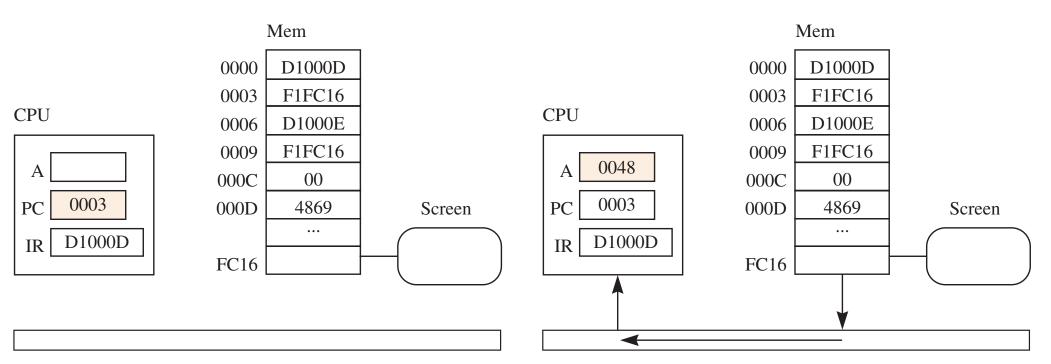

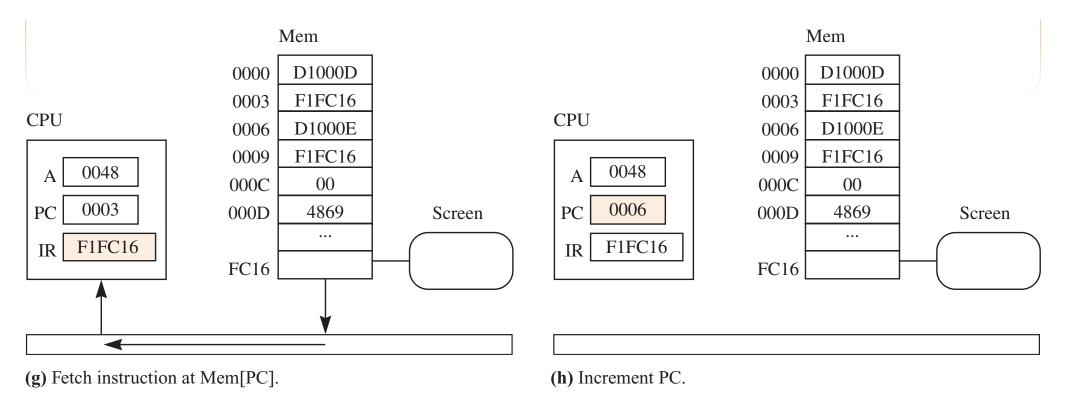

# The von Neumann execution cycle

- Fetch instruction at Mem[PC].

- Decode instruction fetched.

- Increment PC.

- Execute the instruction fetched.

- Repeat.

Figure 4.31

Load the machine language program Initialize PC and SP

#### do {

Fetch the next instruction Decode the instruction specifier Increment PC Execute the instruction fetched

#### }

while (the stop instruction does not execute)

Load the machine language program into memory starting at address 0000  $PC \leftarrow 0000$

$SP \leftarrow Mem[FFF4]$

#### do {

Fetch the instruction specifier at address in PC  $\leftarrow$  PC + 1

Decode the instruction specifier

if (the instruction is not unary) {

Fetch the operand specifier at address in PC

PC ← PC + 2

```

} Execute the instruction fetched

```

while ((the stop instruction does not execute) &&

(the instruction is legal))

Figure 4.33

| <u>Address</u> | <u>Mac</u> ł | <u>nine L</u> | angua | ige (b | <u>in)</u> |      |

|----------------|--------------|---------------|-------|--------|------------|------|

| 0000           | 1101         | 0001          | 0000  | 0000   | 0000       | 1101 |

| 0003           | 1111         | 0001          | 1111  | 1100   | 0001       | 0110 |

| 0006           | 1101         | 0001          | 0000  | 0000   | 0000       | 1110 |

| 0009           | 1111         | 0001          | 1111  | 1100   | 0001       | 0110 |

| 000C           | 0000         | 0000          |       |        |            |      |

| 000D           | 0100         | 1000          | 0110  | 1001   |            |      |

| 000F           |              |               |       |        |            |      |

| <u>Address</u> | Machine | <u>e Language (hex)</u>               |

|----------------|---------|---------------------------------------|

| 0000           | D1000D  | ;Load byte accumulator 'H'            |

| 0003           | F1FC16  | ;Store byte accumulator output device |

| 0006           | D1000E  | ;Load byte accumulator 'i'            |

| 0009           | F1FC16  | ;Store byte accumulator output device |

| 000C           | 00      | ;Stop                                 |

| 000D           | 4869    | ;ASCII "Hi" characters                |

<u>Output</u>

Hi

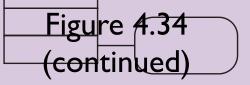

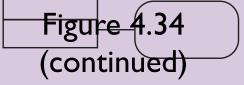

Figure 4.34

(a) Initial state before loading.

Mem

(b) Program loaded into main memory.

(c) PC  $\leftarrow$  0000 (hex).

(e) Increment PC.

(f) Execute. Load byte for H to accumulator.

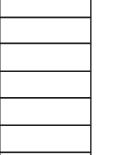

## Figure 4.34 (continued)

CPU

#### Computer Systems

FIFTH EDITION

Screen

Η

Mem

0000

0003

0006

0009

000C

000D

FC16

D1000D

F1FC16

D1000E

F1FC16

00

4869

•••

48

(i) Execute. Store byte from accumulator to output device.

CPU

(j) Fetch instruction at Mem[PC].

0048

0006

D1000E

А

IR

## **Computer Systems**

TH EDITION

(k) Increment PC.

(I) Execute. Load byte for i to accumulator.

Figure 4.35

| <u>Address</u> | <u>Machine Language (bin)</u> |      |      |      |      |      |

|----------------|-------------------------------|------|------|------|------|------|

| 0000           | 1101                          | 0001 | 1111 | 1100 | 0001 | 0101 |

| 0003           | 1111                          | 0001 | 0000 | 0000 | 0001 | 0011 |

| 0006           | 1101                          | 0001 | 1111 | 1100 | 0001 | 0101 |

| 0009           | 1111                          | 0001 | 1111 | 1100 | 0001 | 0110 |

| 000C           | 1101                          | 0001 | 0000 | 0000 | 0001 | 0011 |

| 000F           | 1111                          | 0001 | 1111 | 1100 | 0001 | 0110 |

| 0012           | 0000                          | 0000 |      |      |      |      |

| <u>Address</u> | <b>Machine</b> | <u> Language (hex)</u>   |

|----------------|----------------|--------------------------|

| 0000           | D1FC15         | ;Input first character   |

| 0003           | F10013         | ;Store first character   |

| 0006           | D1FC15         | ;Input second character  |

| 0009           | F1FC16         | ;Output second character |

| 000C           | D10013         | ;Load first character    |

| 000F           | F1FC16         | ;Output first character  |

| 0012           | 00             | ;Stop                    |

<u>Input</u>

up

#### <u>Output</u>

pu

Figure 4.36

| <u>Address</u> | <u>Machine Language (bin)</u> |      |      |      |      |      |

|----------------|-------------------------------|------|------|------|------|------|

| 0000           | 1100                          | 0001 | 0000 | 0000 | 0000 | 1101 |

| 0003           | 0110                          | 0001 | 0000 | 0000 | 0000 | 1111 |

| 0006           | 1001                          | 0001 | 0000 | 0000 | 0001 | 0001 |

| 0009           | 1111                          | 0001 | 1111 | 1100 | 0001 | 0110 |

| 000C           | 0000                          | 0000 |      |      |      |      |

| 000D           | 0000                          | 0000 | 0000 | 0101 |      |      |

| 000F           | 0000                          | 0000 | 0000 | 0011 |      |      |

| 0011           | 0000                          | 0000 | 0011 | 0000 |      |      |

| <u>Address</u> | <u>Machine Language (hex)</u> |                           |  |  |

|----------------|-------------------------------|---------------------------|--|--|

| 0000           | C1000D                        | ;A <- first number        |  |  |

| 0003           | 61000F                        | ;Add the two numbers      |  |  |

| 0006           | 910011                        | ;Convert sum to character |  |  |

| 0009           | F1FC16                        | ;Output the character     |  |  |

| 000C           | 00                            | ;Stop                     |  |  |

| 000D           | 0005                          | ;Decimal 5                |  |  |

| 000F           | 0003                          | ;Decimal 3                |  |  |

| 0011           | 0030                          | ;Mask for ASCII char      |  |  |

#### <u>Output</u>

8

Figure 4.37

| <u>Address</u> | Mach | <u>Machine Language (bin)</u> |      |      |      |      |  |

|----------------|------|-------------------------------|------|------|------|------|--|

| 0000           | 1101 | 0001                          | 0000 | 0000 | 0001 | 1001 |  |

| 0003           | 1111 | 0001                          | 0000 | 0000 | 0000 | 1001 |  |

| 0006           | 1100 | 0001                          | 0000 | 0000 | 0001 | 0011 |  |

| 0009           | 0110 | 0001                          | 0000 | 0000 | 0001 | 0101 |  |

| 000C           | 1001 | 0001                          | 0000 | 0000 | 0001 | 0111 |  |

| 000F           | 1111 | 0001                          | 1111 | 1100 | 0001 | 0110 |  |

| 0012           | 0000 | 0000                          |      |      |      |      |  |

| 0013           | 0000 | 0000                          | 0000 | 0101 |      |      |  |

| 0015           | 0000 | 0000                          | 0000 | 0011 |      |      |  |

| 0017           | 0000 | 0000                          | 0011 | 0000 |      |      |  |

| 0019           | 0111 | 0001                          |      |      |      |      |  |

Figure 4.37 (continued)

| <u>Address</u> | Machine | <u>e Language (hex)</u>     |

|----------------|---------|-----------------------------|

| 0000           | D10019  | ;Load byte accumulator      |

| 0003           | F10009  | ;Store byte accumulator     |

| 0006           | C10013  | ;A <- first number          |

| 0009           | 610015  | ;Add the two numbers        |

| 000C           | 910017  | ;Convert sum to character   |

| 000F           | F1FC16  | ;Output the character       |

| 0012           | 00      | ;Stop                       |

| 0013           | 0005    | ;Decimal 5                  |

| 0015           | 0003    | ;Decimal 3                  |

| 0017           | 0030    | ;Mask for ASCII char        |

| 0019           | 71      | ;Byte to modify instruction |

<u>Output</u>

2

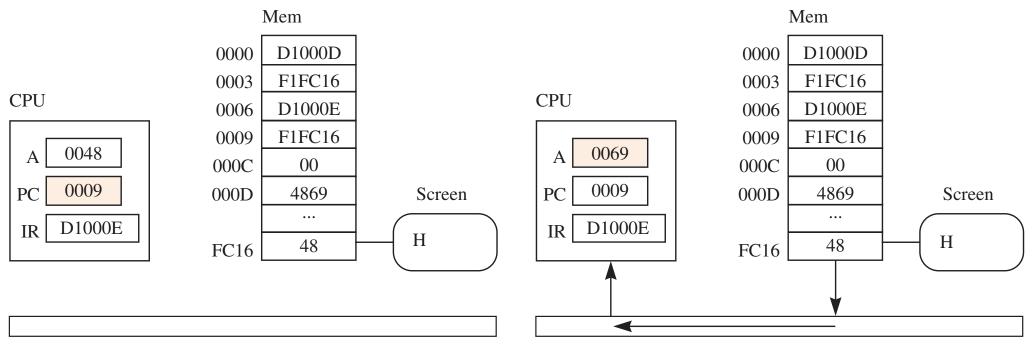

# Intel x-86 computer architecture

Figure 4.38

Copyright © 2017 by Jones & Bartlett Learning, LLC an Ascend Learning Company

| Status Bit | Intel Name | <b>EFLAGS</b> Position |

|------------|------------|------------------------|

| Ν          | SF         | 7                      |

| Ζ          | ZF         | 6                      |

| V          | OF         | 11                     |

| С          | CF         | 0                      |

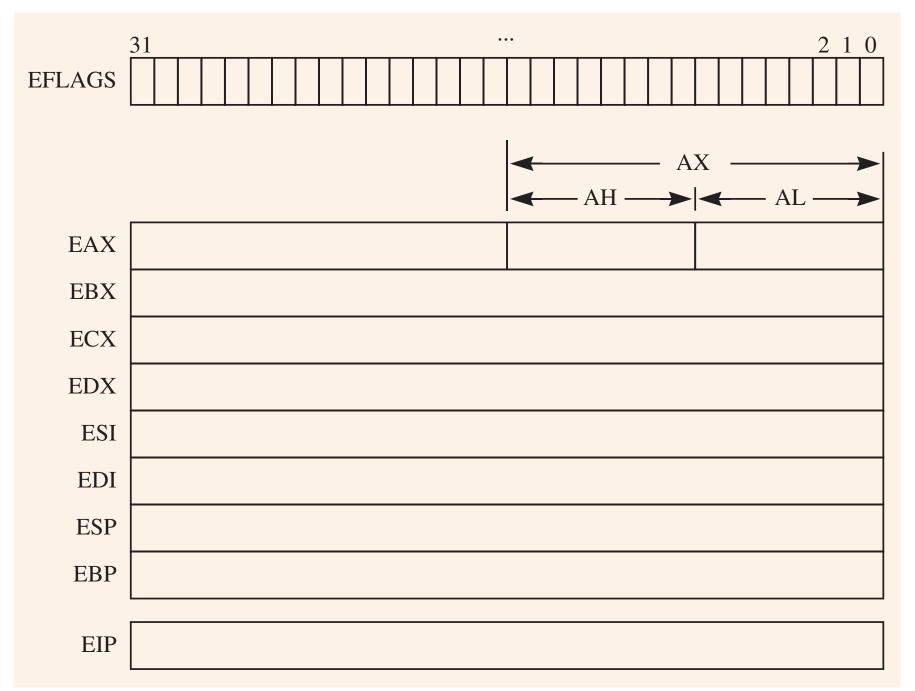

# x86 add register instruction

# Memory devices

- Read/Write memory

- Also called Random-Access Memory (RAM)

- Can load from RAM and store to RAM

- Read-Only memory (ROM)

- Can load from ROM

- Cannot store to ROM

- RAM and ROM are both random

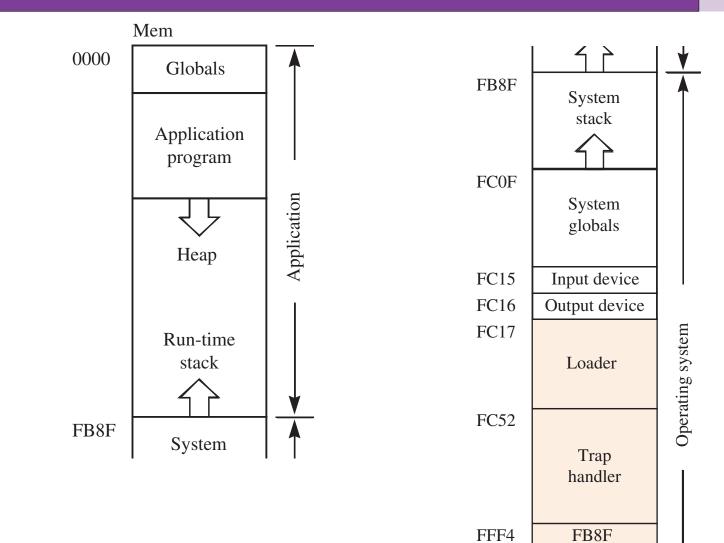

#### Figure 4.41

FFF6

FFF8

FFFA FFFC

FFFE

FC0F

FC15 FC16

FC17

FC52

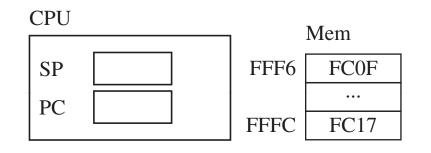

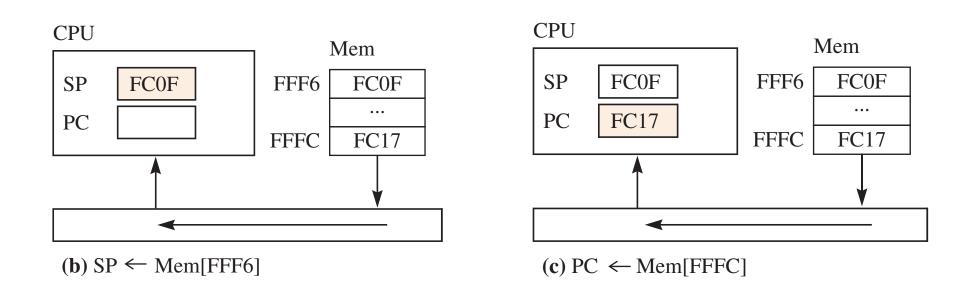

## The load option

- SP ← Mem[FFF6]

- PC ← Mem[FFFC]

- Start the von Neumann cycle

Figure 4.42

(a) Initial state.

Copyright © 2017 by Jones & Bartlett Learning, LLC an Ascend Learning Company

## The execute option

- SP ← Mem[FFF4]

- PC ← 0000

- Start the von Neumann cycle

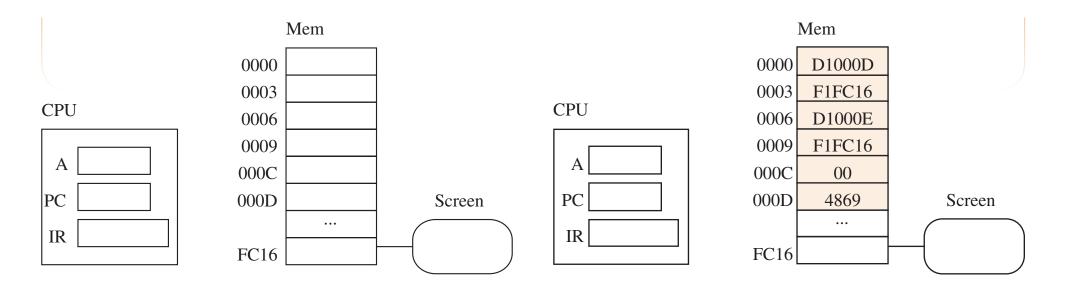

| Figure | 4.43 |

|--------|------|

|--------|------|

| <u>Address</u> | <u>Machine</u> | <u>e Language (hex)</u>               |

|----------------|----------------|---------------------------------------|

| 0000           | D1000D         | ;Load byte accumulator 'H'            |

| 0003           | F1FC16         | ;Store byte accumulator output device |

| 0006           | D1000E         | ;Load byte accumulator 'i'            |

| 0009           | F1FC16         | ;Store byte accumulator output device |

| 000C           | 00             | ;Stop                                 |

| 000D           | 4869           | ;ASCII "Hi" characters                |

#### Hex Version for the Loader

D1 00 0D F1 FC 16 D1 00 0E F1 FC 16 00 48 69 zz

#### <u>Output</u>

Hi